A latch is an example of a bistable multivibrator, that is, a device with exactly two stable states. These states are high-output and low-output. A latch has a feedback path, so information can be retained by the device. Therefore latches can be memory devices, and can store one bit of data for as long as the device is powered. As the name suggests, latches are used to "latch onto" information and hold in place. Latches are very similar to flip-flops, but are not synchronous devices, and do not operate on clock edges as flip-flops do.

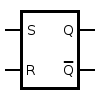

SR latch

An SR latch (Set/Reset) is an asynchronous device: it works independently of control signals and relies only on the state of the S and R inputs. In the image we can see that an SR latch can be created with two NOR gates that have a cross-feedback loop. SR latches can also be made from NAND gates, but the inputs are swapped and negated. In this case, it is sometimes called an SR latch.

When a high is applied to the Set line of an SR latch, the Q output goes high (and Q low). The feedback mechanism, however, means that the Q output will remain high, even when the S input goes low again. This is how the latch serves as a memory device. Conversely, a high input on the Reset line will drive the Q output low (and Q high), effectively resetting the latch's "memory". When both inputs are low, the latch "latches" – it remains in its previously set or reset

When both inputs are high at once, however, there is a problem: it is being told to simultaneously produce a high Q and a low Q. This produces a "race condition" within the circuit - whichever flip flop succeeds in changing first will feedback to the other and assert itself. Ideally, both gates are identical and this is "metastable", and the device will be in an undefined state for an indefinite period. In real life, due to manufacturing methods, one gate will always win, but it's impossible to tell which it will be for a particular device from an assembly line. The state of S = R = 1 is therefore "illegal" and should never be entered.

| S | R | Q | Q | |

|---|---|---|---|---|

| 0 | 0 | Latch | ||

| 0 | 1 | 0 | 1 | |

| 1 | 0 | 1 | 0 | |

| 1 | 1 | Metastable | ||

When the device is powered up, a similar condition occurs, because both outputs, Q and Q, are low. Again, the device will quickly exit the metastable state due to differences between the two gates, but it's impossible to predict which of Q and Q will end up high. To avoid spurious actions, you should always set SR flip-flops to a known initial state before using them - you must not assume that they will initialise to a low state.

Gated SR latch

In some situations it may be desirable to dictate when the latch can and cannot latch. The gated SR latch is a simple extension of the SR latch which provides an Enable line which must be driven high before data can be latched. Even though a control line is now required, the SR latch is not synchronous, because the inputs can change the output even in the middle of an enable pulse.

When the Enable input is low, then the outputs from the AND gates must also be low, thus the Q and Q outputs remain latched to the previous data. Only when the enable input is high can the state of the latch change, as shown in the truth table. When the enable line is asserted, a gated SR latch is identical in operation to an SR latch.

The Enable line is sometimes a clock signal, but is usually a read or write strobe.

| Enable | S | R | Q | Q | |

|---|---|---|---|---|---|

| 0 | 0 | 0 | Latch | ||

| 0 | 0 | 1 | Latch | ||

| 0 | 1 | 0 | Latch | ||

| 0 | 1 | 1 | Latch | ||

| 1 | 0 | 0 | Latch | ||

| 1 | 0 | 1 | 0 | 1 | |

| 1 | 1 | 0 | 1 | 0 | |

| 1 | 1 | 1 | Metastable | ||

D latch

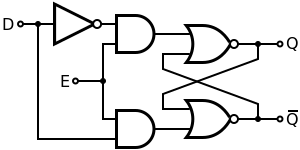

The D latch (D for "data") or transparent latch is a simple extension of the gated SR latch that removes the possibility of invalid input states.

Since the gated SR latch allows us to latch the output without using the S or R inputs, we can remove one of the inputs by driving both the Set and Reset inputs with a complementary driver: we remove one input and automatically make it the inverse of the remaining input.

The D latch outputs the D input whenever the Enable line is high, otherwise the output is whatever the D input was when theEnable input was last high. This is why it is also known as a transparent latch - when Enable is asserted, the latch is said to be "transparent" - it signals propagate directly through it as if it isn't there.

| Enable | D | Q | Q | |

|---|---|---|---|---|

| 0 | 0 | Latch | ||

| 0 | 1 | Latch | ||

| 1 | 0 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

D latches are often used in I/O ports of integrated circuits and are available as discrete devices, often multiply packaged. An example is the 74HC75, part of the 7400 series of ICs, containing four separate D latches.

No comments:

Post a Comment